设备控制器的基本功能

控制器的作用是控制和协调整个计算机的动作控制通常需要程式计数器(PC)、指令暂存器(IR)、指令解码器(ID)、定时与控制电路以及脉冲源、中断等共同完成。控制器由:指令暂存器Instruction Register、指令解码器Instruction Decoder、定时与控制电路Programmable Logic Array、程式计数器Program Counter、标誌暂存器Flags Register、堆叠和堆叠指针Stack Pointer、暂存器组等构成。

接收和识别命令

CPU可以向控制器传送多种不同的命令,设备控制器应能接收并识别这些命令。为此,在控制器中应具有相应的控制暂存器,用来存放接收的命令和参数,并对所接收的命令进行解码。例如,磁碟控制器可以接收CPU发来的Read、Write、Format等15条不同的命令,而且有些命令还带有参数;相应地,在磁碟控制器中有多个暂存器和命令解码器等。

设备控制器的组成

设备控制器的组成数据交换

这是指实现CPU与控制器之间、控制器与设备之间的数据交换。对于前者,是通过数据汇流排,由CPU并行地把数据写入控制器,或从控制器中并行地读出数据;对于后者,是设备将数据输入到控制器,或从控制器传送给设备。为此,在控制器中须设定数据暂存器。

标识和报告设备的状态

控制器应记下设备的状态供CPU了解。例如,仅当该设备处于传送就绪状态时,CPU才能启动控制器从设备中读出数据。为此,在控制器中应设定一状态暂存器,用其中的每一位来反映设备的某一种状态。当CPU将该暂存器的内容读入后,便可了解该设备的状态。

地址识别

就像记忆体中的每一个单元都有一个地址一样,系统中的每一个设备也都有一个地址,而设备控制器又必须能够识别它所控制的每个设备的地址。此外,为使CPU能向(或从)暂存器中写入(或读出)数据,这些暂存器都应具有唯一的地址。例如,在IB-MPC机中规定,硬碟控制器中各暂存器的地址分别为320~32F之一。控制器应能正确识别这些地址,为此,在控制器中应配置地址解码器。

数据缓冲

由于I/O设备的速率较低而CPU和记忆体的速率却很高,故在控制器中必须设定一缓冲器。在输出时,用此缓冲器暂存由主机高速传来的数据,然后才以I/O设备所具有的速率将缓冲器中的数据传送给I/O设备;在输入时,缓冲器则用于暂存从I/O设备送来的数据,待接收到一批数据后,再将缓冲器中的数据高速地传送给主机。

差错控制

设备控制器还兼管对由I/O设备传送来的数据进行差错检测。若发现传送中出现了错误,通常是将差错检测码置位,并向CPU报告,于是CPU将本次传送来的数据作废,并重新进行一次传送。这样便可保证数据输入的正确性。

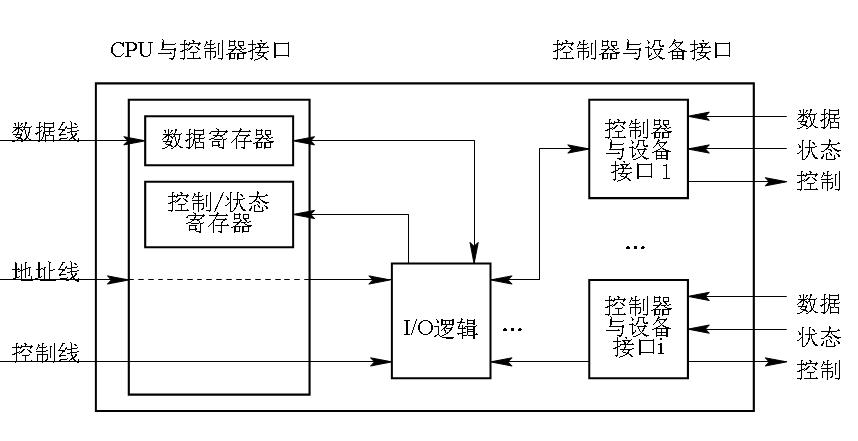

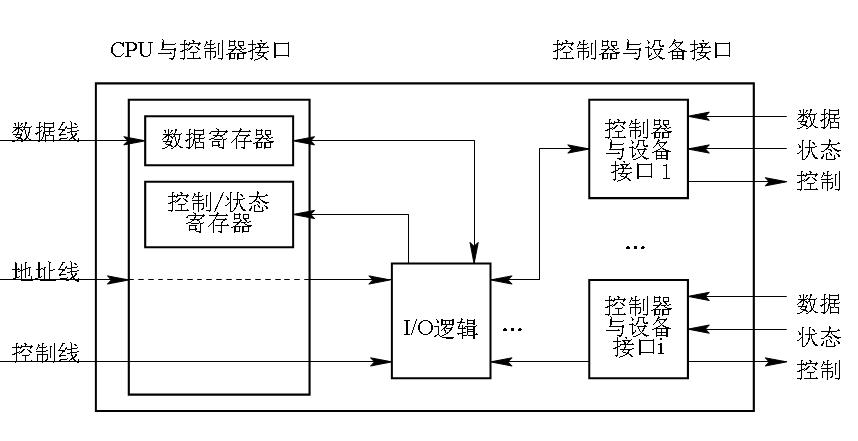

设备控制器的组成

设备控制器与处理机的接口

该接口用于实现CPU与设备控制器之间的通信。共有三类信号线: 数据线、地址线和控制线。数据线通常与两类暂存器相连线,第一类是数据暂存器(在控制器中可以有一个或多个数据暂存器,用于存放从设备送来的数据(输入)或从CPU送来的数据(输出));第二类是控制/状态暂存器(在控制器中可以有一个或多个这类暂存器,用于存放从CPU送来的控制信息或设备的状态信息)。

设备控制器与设备的接口

在一个设备控制器上,可以连线一个或多个设备。相应地,在控制器中便有一个或多个设备接口,一个接口连线一台设备。在每个接口中都存在数据、控制和状态三种类型的信号。控制器中的I/O逻辑根据处理机发来的地址信号去选择一个设备接口。

I/O逻辑

在设备控制器中的I/O逻辑用于实现对设备的控制。它通过一组控制线与处理机互动,处理机利用该逻辑向控制器传送I/O命令;I/O逻辑对收到的命令进行解码。每当CPU要启动一个设备时,一方面将启动命令传送给控制器;另一方面又同时通过地址线把地址传送给控制器,由控制器的I/O逻辑对收到的地址进行解码,再根据所译出的命令对所选设备进行控制。

设备控制器的组成

设备控制器的组成