真值表及符号

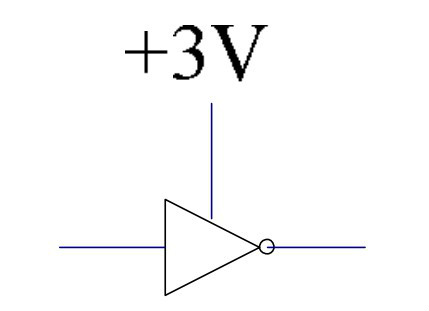

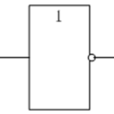

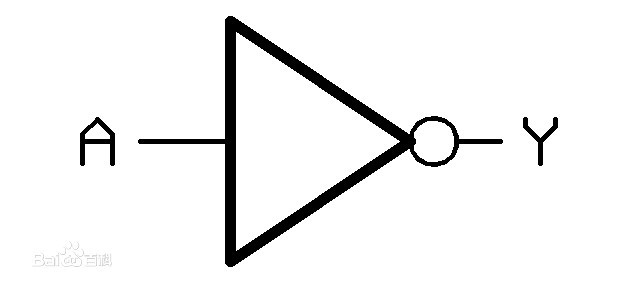

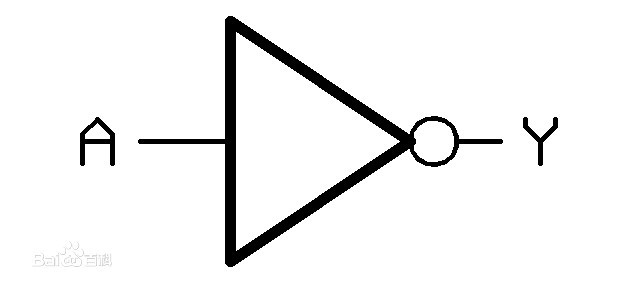

能实现非逻辑功能的电路称为非门电路,又称反相器,简称非门。下列包括“非”门的2种符号。

ANSI/IEEE Std 91-1984

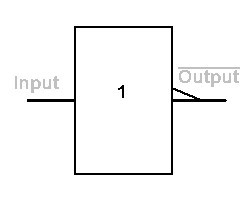

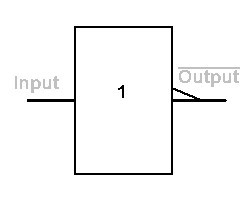

ANSI/IEEE Std 91-1984 IEC 60617-12

IEC 60617-12图形符号:

形状特徵型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)。

软体中符号:NOT/7404

真值表:

具体实现

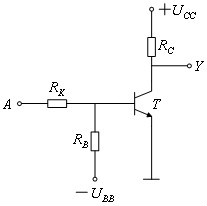

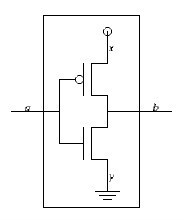

设计一:利用三极体进行非门的实现

电晶体“非”门电路不同于放大电路,管子的工作状态或从截止转为饱和,或从饱和转为截止。“非”门电路只有一个输入端A,当A为“1”(设其电位为3V)时,电晶体饱和,其集电极,即输出端Y为“0”(其电位在零伏附近);当A为“0”时,电晶体截止,输出端Y为“1”(其电位近似等于

)。所以“非”门电路也称为反相器。加负电源

是为了使电晶体可靠截止。

图中,

是“非”门的门电阻,其作用是通过它向输出端提供电压。T饱和,

上产生很大的压降,使集电极电位几乎与发射极的电位相等;截止时,

通过

加到集电极上,使集电极电压等于

。

是输入电阻,通过它给T加正向偏置电流,即输入信号。

是反偏电阻,通过它给T加反向偏置电流。这两个电阻配合得当,才可以使输入“1”时T饱和导通,输入“0”时T可靠截止。

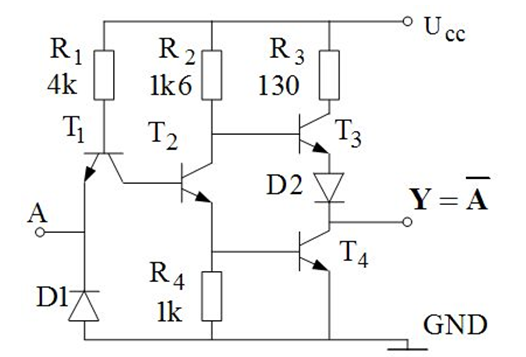

设计二:TTL非门电路的实现

这里T1不是当成三极体使用的,而是具有一个正极、两个负极的特殊二极体。因为一般三极体发射结有电流时,就产生大很多倍的电流流进管子。这里T1“发射结”有电流时,集电极根本无电流。"发射结”有电流时,集电极产生电流流出管子。

从4kΩ电阻到T1的“集电结”,到T2的发射结,再到1kΩ电阻,实际是两只电阻、两只PN结组成的串联分压电路,在这个迴路中,越往下电位就越低。所以T1的基极电位总是高于集电极0.7V的。PN结正向压降0.7V,两只PN结正向压降1.4V,那幺两只电阻压降为(5-1.4)V=3.6V,4kΩ电阻压降为[4/(4+1)]×3.6V≈2.9V,故T1集电极电压为5-2.9-0.7=1.4V。

A端输入3.6V以上高电平电压时,T1集电极1.4V电压低于发射极电压,4kΩ电阻电流经T1集点结流向T2发射结,使T2饱和,T4饱和,电路输出低电平。

A端输入1V以下低电平电压时,T

1发射极电压低于集电极1.4V电压,4kΩ电阻电流经T

1发射结流向低电平输入端A,T

2得不到电流而截止,T

4截止,

经R

2使T

3饱和导通,电路输出高电平,实现非逻辑关係。

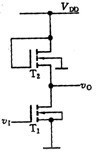

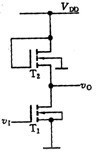

设计三:利用CMOS逻辑进行非门的实现

两管的栅极相连作为输入端,两管的漏极相连作为输出端。TN的源极接地,TP的源极接电源。为了保证电路正常工作,VDD需要大于TN管开启电压VTN和TP管开启电压VTP的绝对值的和,即UDD > UTN + |UTP|。当Ui=0V时,TN截止,TP导通,Uo≈UDD为高电平;当Ui=UDD时,TN导通,TP截止,Uo≈0V为低电平。因此实现了非逻辑功能。

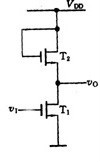

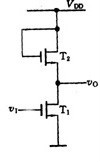

设计四:利用NMOS逻辑进行非门的实现

NMOS逻辑门电路是全部由N沟道MOSFET构成。由于各种器件具有较小的几何尺寸,适合于製造大规模积体电路。此外,由于NMOS积体电路的结构简单,易于使用CAD技术进行设计。与CMOS电路相似,NMOS电路中不使用难于製造的电阻。NMOS反相器是整个NMOS逻辑门电路的基本构件,它的工作管常用增强型器件,而负载管可以是增强型也可以是耗尽型。现以增强型器件作为负载管的NMOS反相器为例来说明它的工作原理。

(a)实际电路

(a)实际电路 (b)简化画法

(b)简化画法图(a)表示NMOS反相器的原理电路,其中为工作管,为负载管,二者均属增强型器件。若和在同一工艺过程中製成,它们必将具有相同的开启电压VT。图(b)是它的简化画法。负载管的栅极与漏极同接电源,因而总是工作在它的恆流区,处于导通状态。

当输入为高电压(超过管子的开启电压VT)时,导通,输出为低电压。输出低电压的值由、两管导通时所呈现的电阻值之比决定。通常的跨导gm1远大于管的跨导gm2,以保证输出低电压值在 1V左右。当输入电压为低电压(低于管子的开启电压VT)时,截止,输出为高电压。由于管总是处于导通状态,因此输出高电压值约为(VDD-VT)。通常gm1在100~200μS之间,而gm2约为5~15μS。导通时的等效电阻Rds1约为3~10kΩ,而的Rds2约在100~200kΩ之间。负载管导通电阻是随工作电流而变化的非线性电阻。

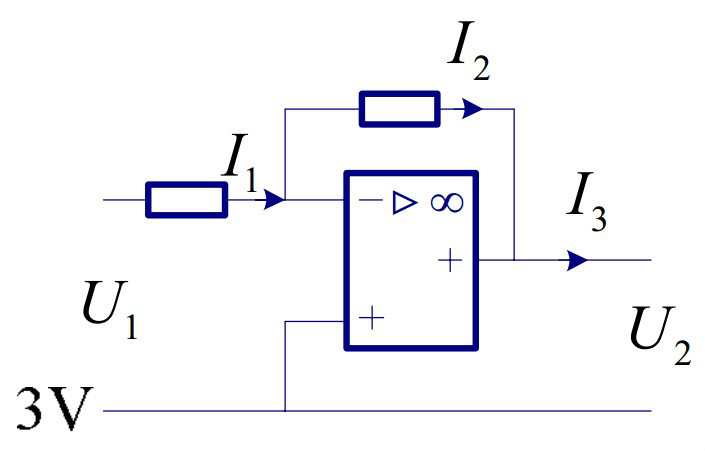

设计五:利用理想运算放大器进行非门的实现

由“虚断”概念,可知

,而又由“虚短”可知运放器输入端电压为零。设两个电阻的阻值相等,则可以得到方程:

于是可得,当左端输入为+6V 时,右端输出为 0V;当左端输入为 0V时,右端输出为+6V。于是达到了非门的作用。

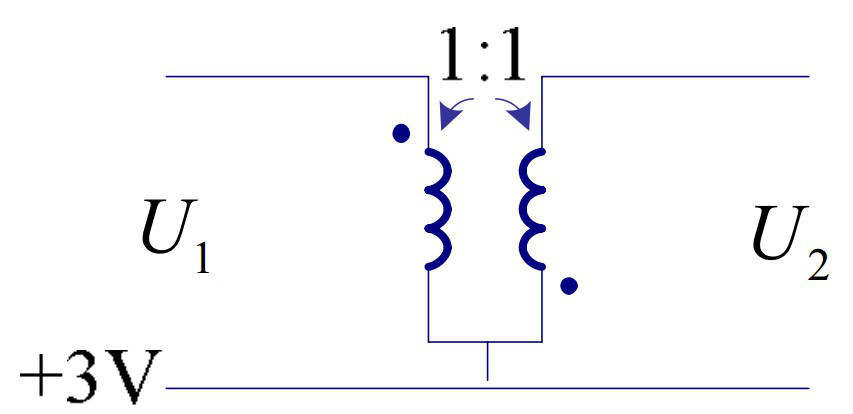

设计六:利用变压器进行非门的实现

利用理想变压器的特性,可以发现,于是,当左端输入电压为+6V,右端的输出电压为 0V;当左端输入电压为 0V,右端的输出电压为+6V。由此达到了非门的作用。

由上述设计可以发现,将非门利用连线埠电路取代的话,为下图所示:

积体电路

非门是基本的逻辑门,因此在TTL和CMOS积体电路中都是可以使用的。标準的积体电路有74X04和CD4049。74X04TTL晶片有14个引脚,4049CMOS晶片有16个引脚,两种晶片都各有2个引脚用于电源供电/基準电压,12个引脚用于6个反相器的输入和输出(4049有2个引脚悬空)。

在数字电路中最具代表性的CMOS非门积体电路是CD4069

ANSI/IEEE Std 91-1984

ANSI/IEEE Std 91-1984 IEC 60617-12

IEC 60617-12

(a)实际电路

(a)实际电路 (b)简化画法

(b)简化画法